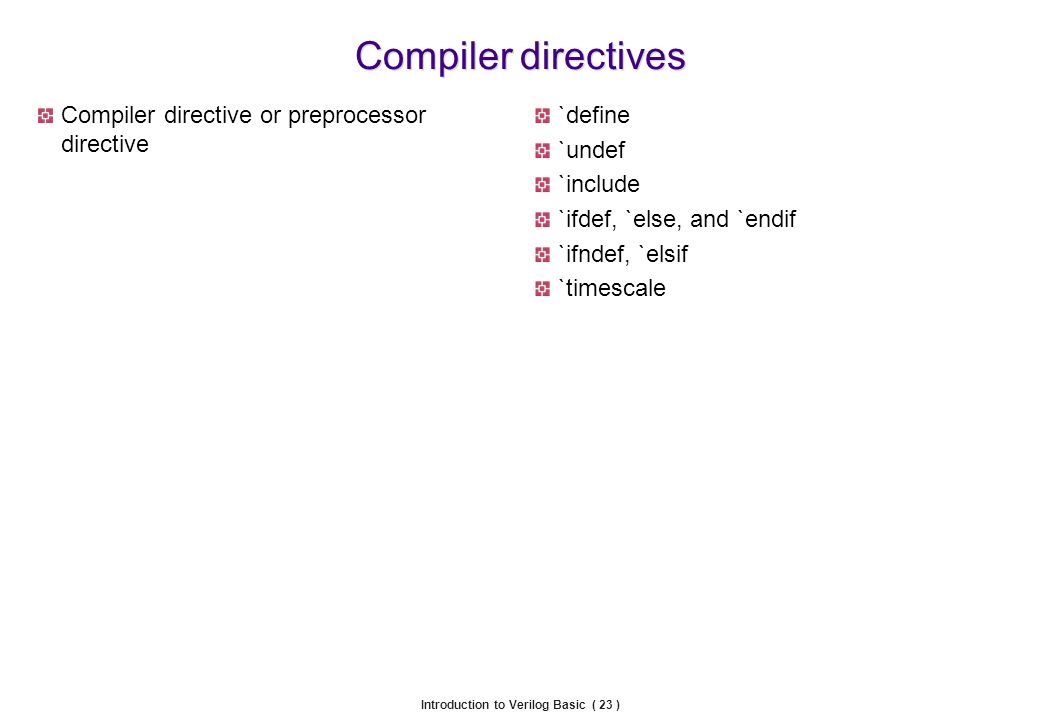

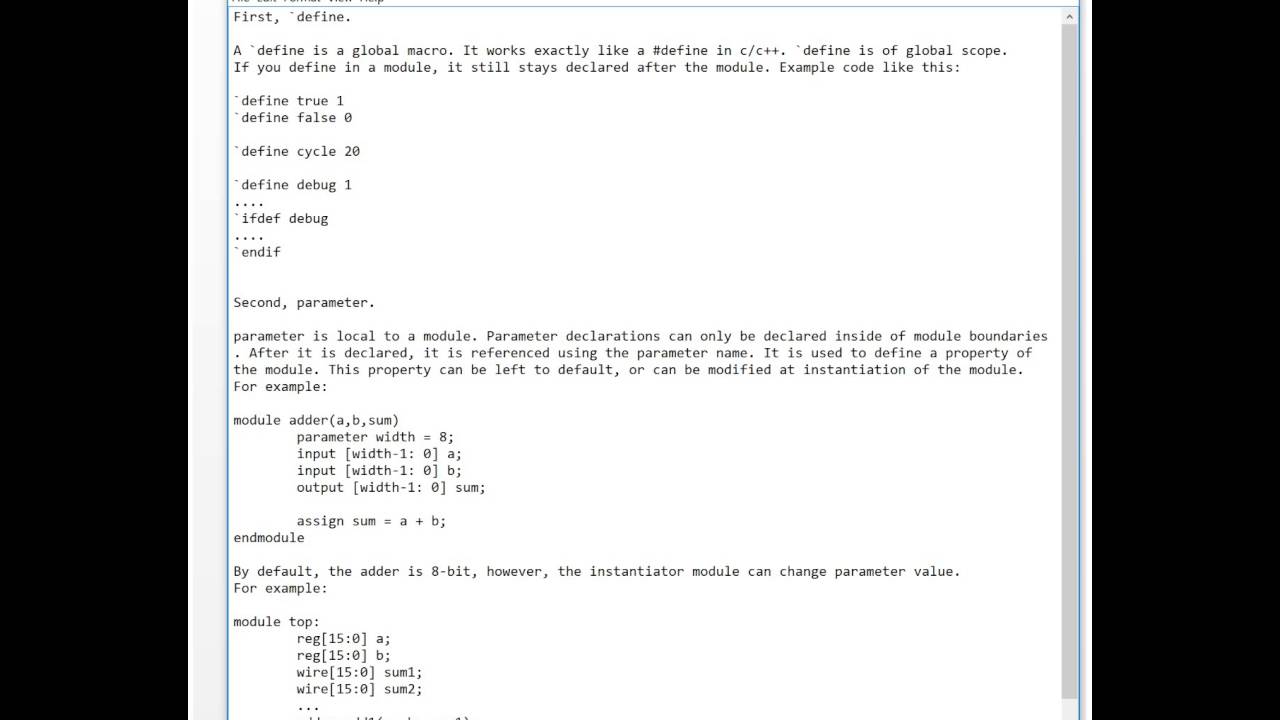

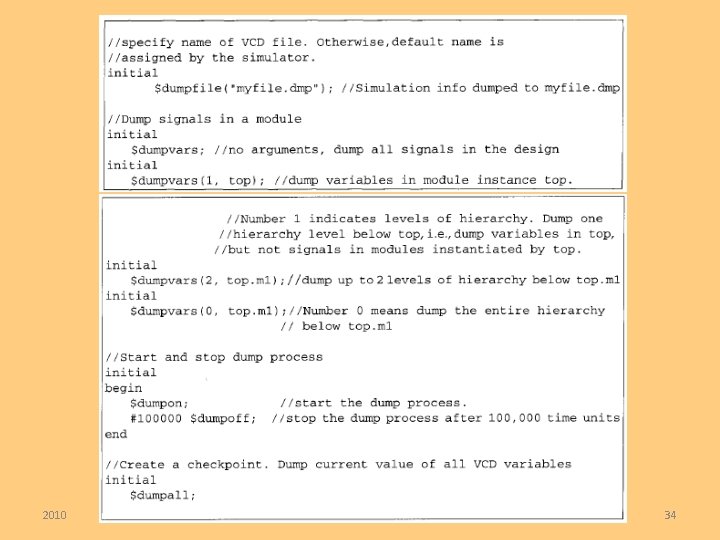

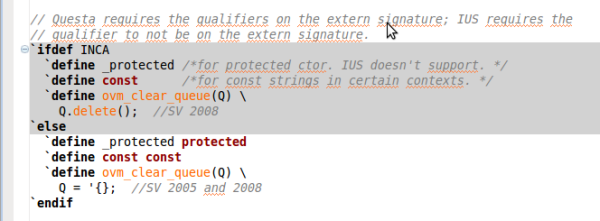

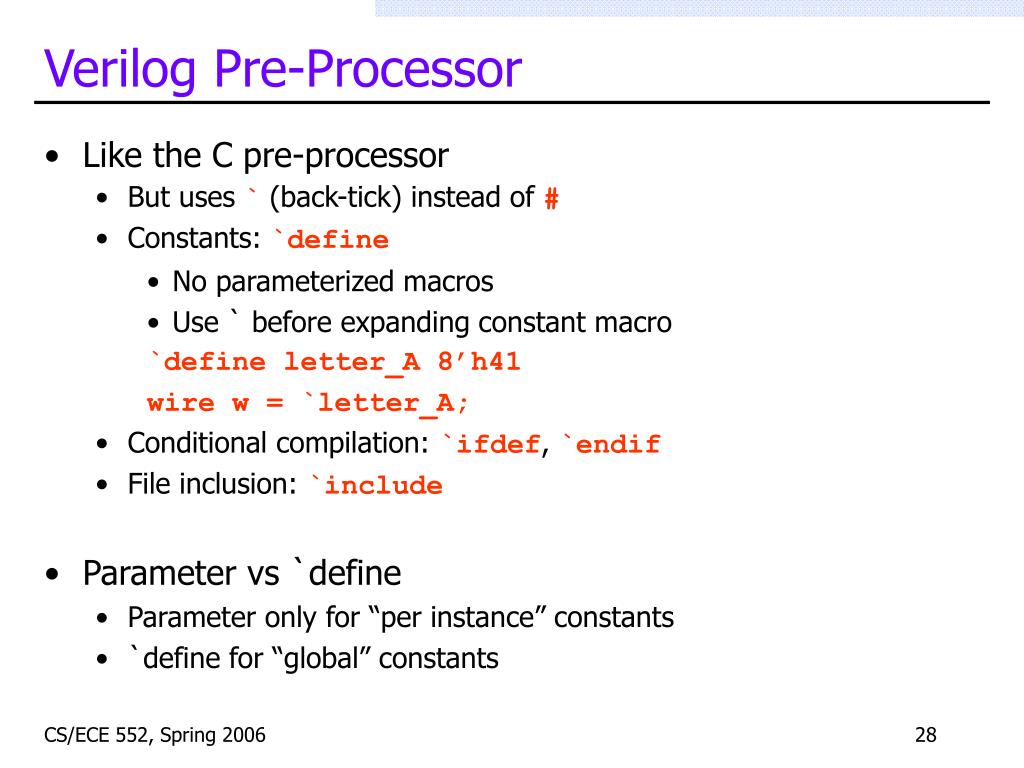

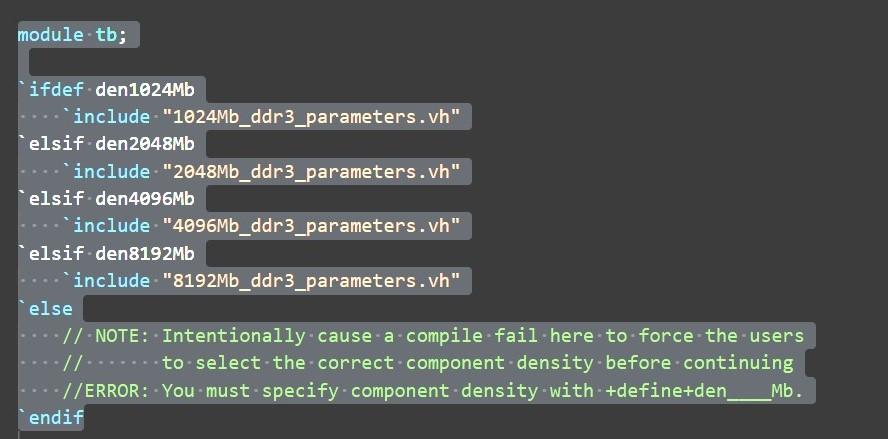

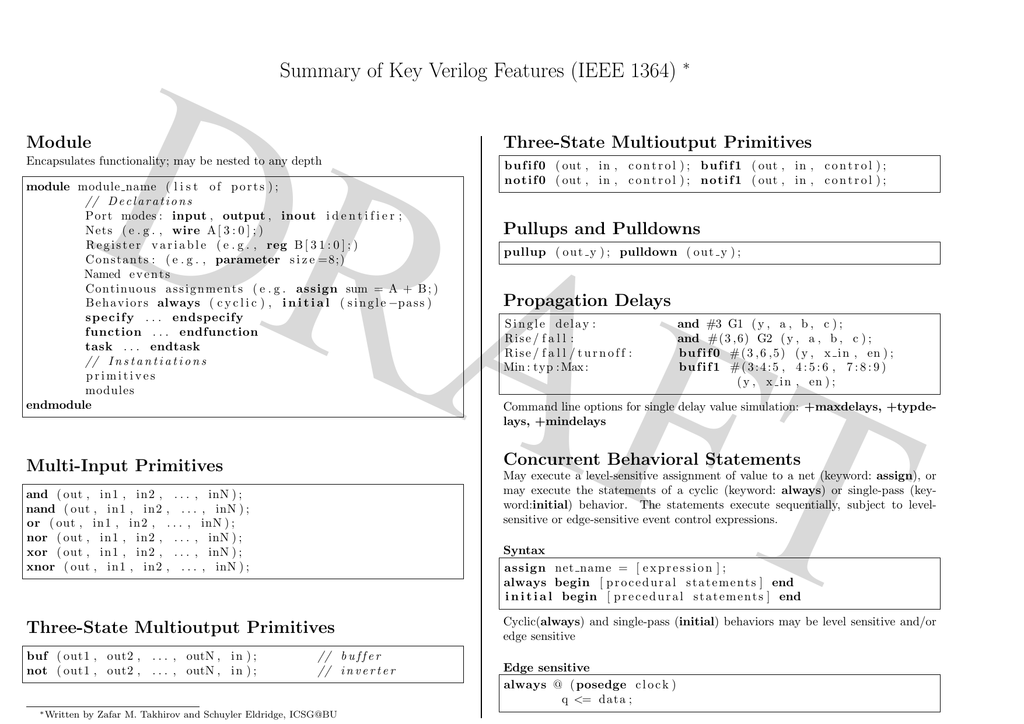

If the macro has not been defined, the compiler compiles the code (if any) following the optional `else directive You can control what code is compiled by choosing whether to define the text macro, either with `define or with define The `endif directive marks the end of the conditional code Example ifdef 1moduleifdef ();

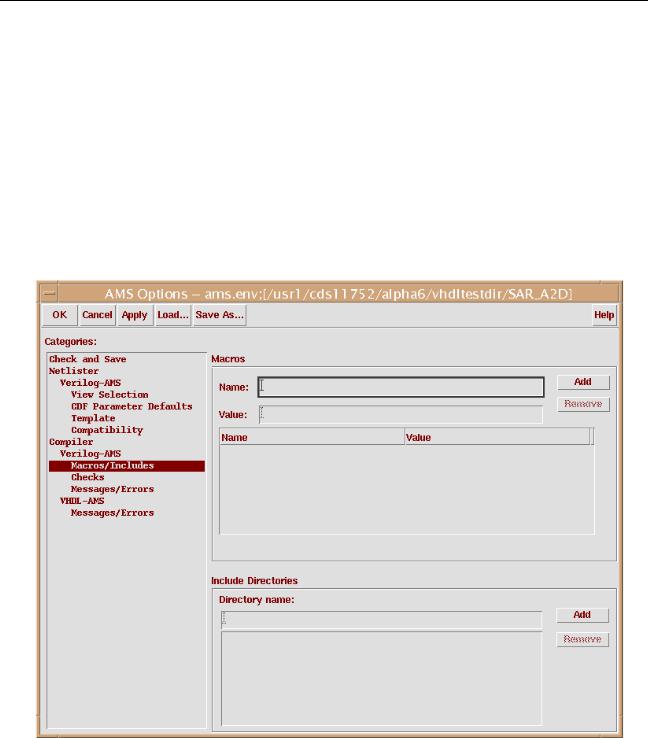

Verilog define parameter 차이- Syntax `ifdef macro_name `endif The macros can either be defined using `define directive or be passed as a parameter with the compile command using the define option `ifndef This directive is just the opposite of the `ifdef directive This directive will compile the underlying code only when the macro is not defined`endif end always @(posedge b)

Verilog define parameter 차이のギャラリー

各画像をクリックすると、ダウンロードまたは拡大表示できます

|  | |

| ||

|  |  |

|  |  |

「Verilog define parameter 차이」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  |  |

|  | |

| ||

「Verilog define parameter 차이」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

|  | |

|  | |

|  |  |

「Verilog define parameter 차이」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  | |

|  |  |

「Verilog define parameter 차이」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  | |

|  | |

|  |  |

「Verilog define parameter 차이」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  |  |

|  |  |

|  |  |

「Verilog define parameter 차이」の画像ギャラリー、詳細は各画像をクリックしてください。

| ||

|  | |

|  | |

| ||

「Verilog define parameter 차이」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  | |

|  | |

|  |  |

「Verilog define parameter 차이」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

| ||

|

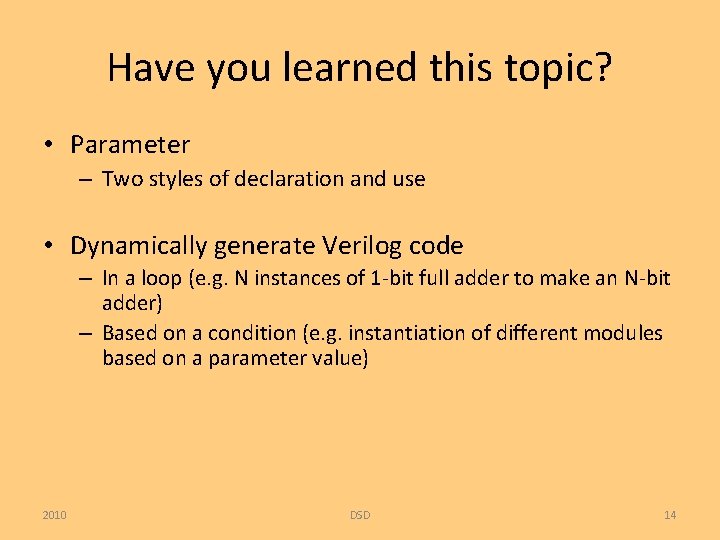

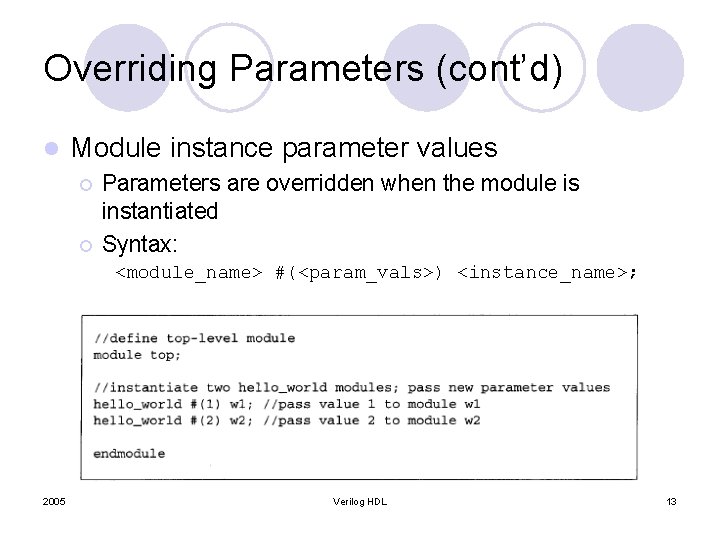

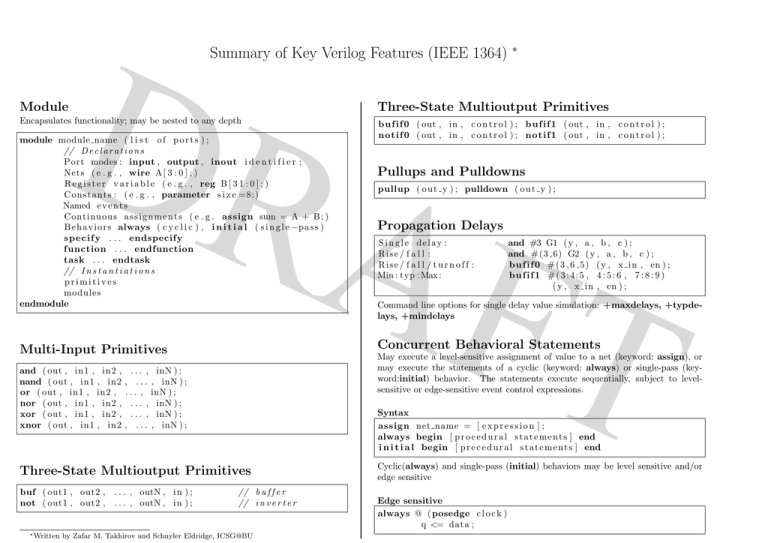

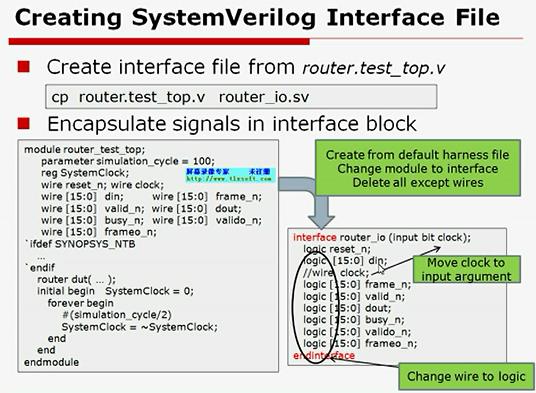

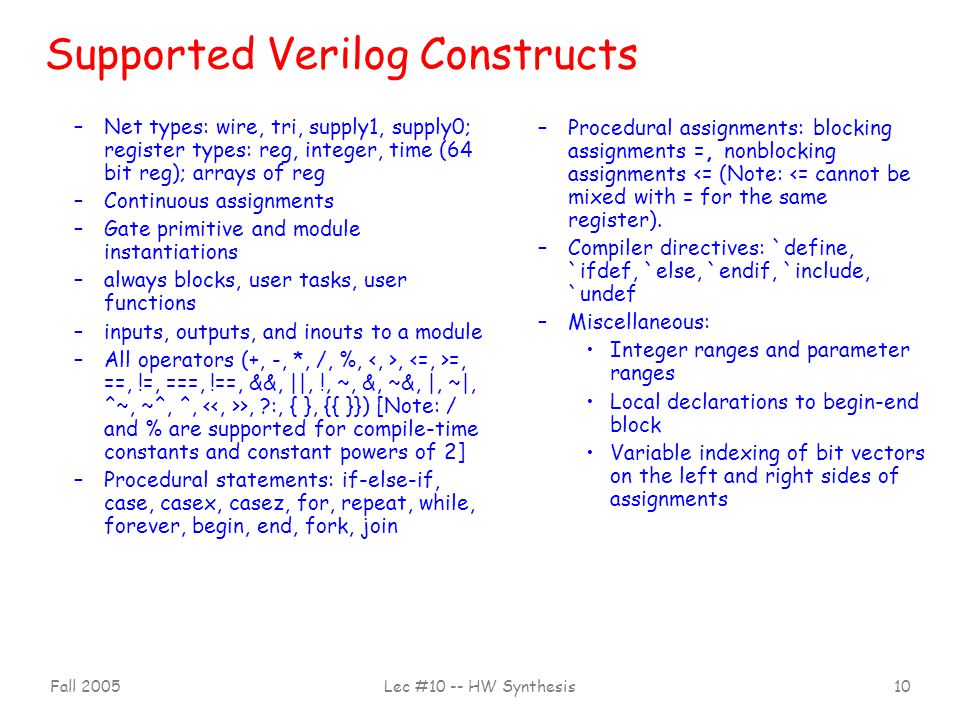

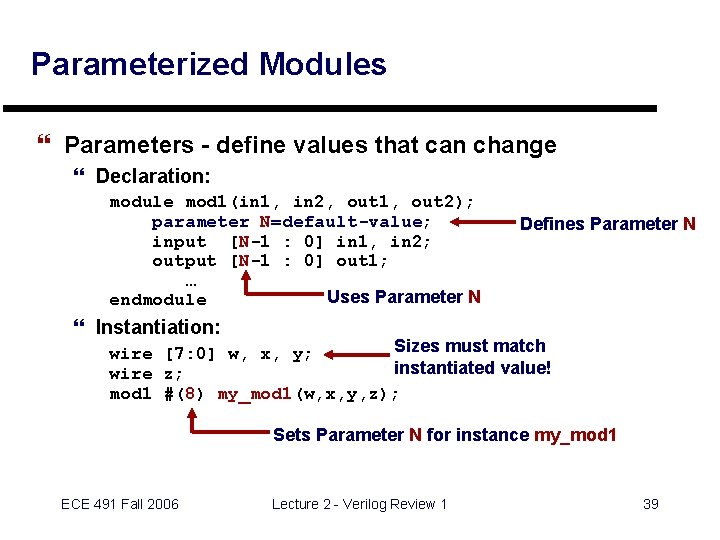

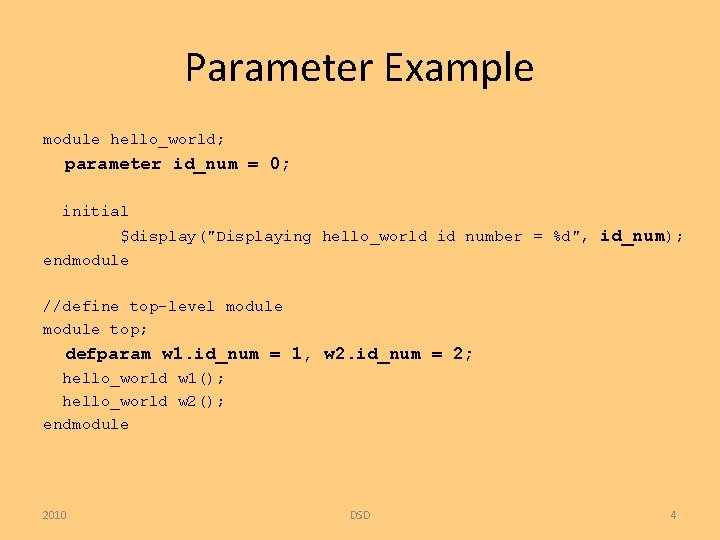

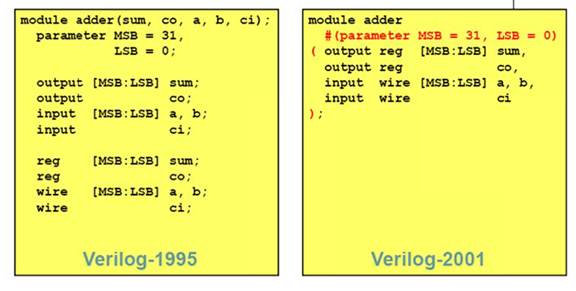

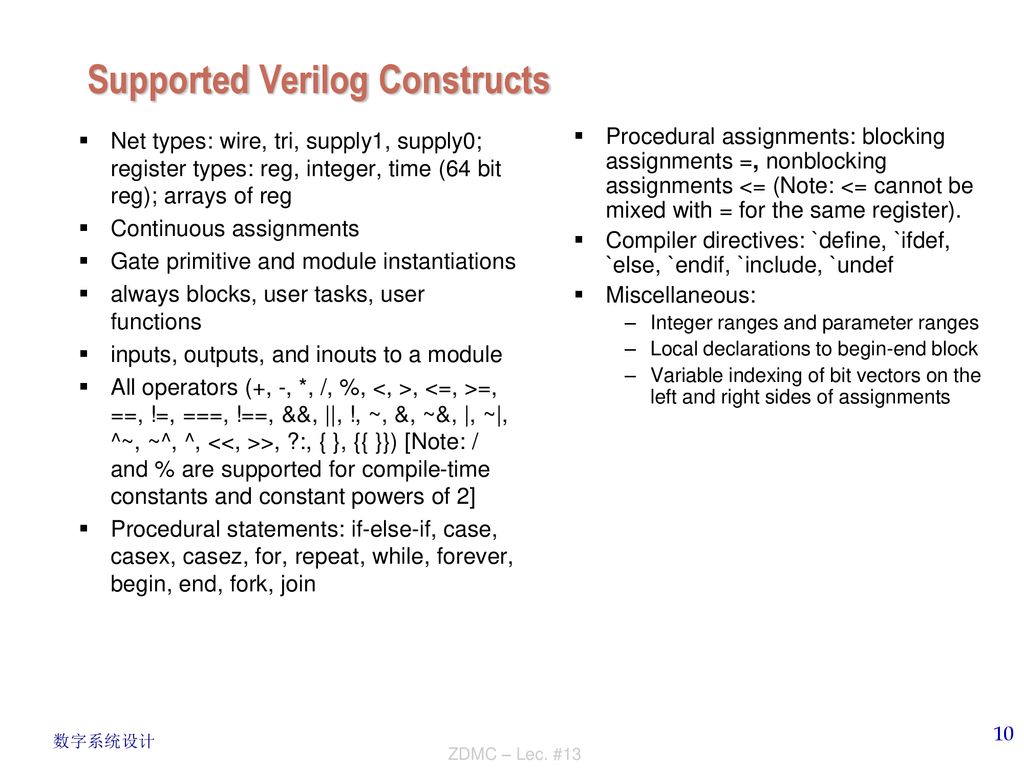

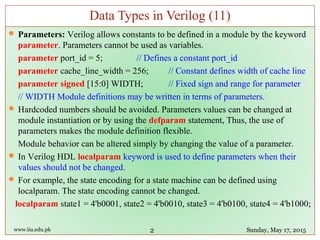

Parameter N = 4;SystemVerilog Parameters define macro must be defined within module boundaries using keyword parameter ifdef can also be used to avoid redefining example

Incoming Term: verilog ifdef parameter, verilog define parameter, verilog define parameterized, system verilog ifdef parameter, verilog define parameter difference, verilog define parameter localparam, verilog define parameter差異, verilog define parameter 違い, verilog define parameter 차이,

0 件のコメント:

コメントを投稿